ソフト編

RSA演算器のマイクロコードの仕様の話になります。

RSA演算器のCPUと呼ぶこともありましたが、一般のCPUと比較するなら、その機能は非常に限られます。

ただCPUで使われる表現を用いたほうが説明が早いということもあり、そういう説明をしていきます。

マイクロコードは32bit×512ワードで、ほぼ水平コードです。

水平コードにしたほうがデコードのディレイがなく組み合わせにより、様々な機能が実現できます。

複数の処理を1ワードでしたり、予想もしなかった機能があとから発見されたりしました。

マイクロコードを格納するメモリは「レジスタファイル」と呼ばれるものでLSIのどの場所にも実装できる反面、

実装面積が大きく大容量化が難しかった。

32bitの幅に抑えるため1bitに複数の意味を割り当てることもしています。

そのbitをONにして複数の機能が動作しても、必要とした機能の実行に悪影響がでなければ、いいという考え方です。

ループ専用の10bitのレジスタI,Jがあり、Jレジスタにいたっては代入できる数字も256、512、1024だけという非常に限定されたものです。

サブルーチンも使えますがスタックが1段しかないのでサブルーチンのなかでサブルーチンは呼べません。

分岐命令は1サイクルの遅延分岐です。分岐命令の直後の1ワードを有効利用するコードを書くようにします。

レジスタに直交性という概念は、全くありません。

レジスタが1024bitで、一般のCPUと比較して非常に大きいため、なるべく少ない機能にして配線数を少なくすることが重要だからです。

詳しいことは開発時に作成した「剰余演算器μコード設計仕様」にあります。

ただ仕様書にあるサンプルのコードは、仕様を作成したときのコードなので、製品版までに改良が進み、製品版のほうがいいものになっています。

「剰余演算器μコード設計仕様」

リンクする際は、PDFへの直リンクでなく、このページにリンクをしていただけますよう、お願い致します。

柔軟だったマイクロコード

水平コードにした結果、組み合わせでいろいろな機能が実装できた。

このおかげでICF3のLSIのバージョンアップをすることなくIBM仕様のフルスペックを満たすことができてしまった。

高額なLSIのバージョンアップ費が不要となり、開発工数も大幅に減り、事業に貢献したという話

1999年8月末、IBM仕様のフルスペックを満たすため検討を行い、LSIの論理を変更することを考えていた。

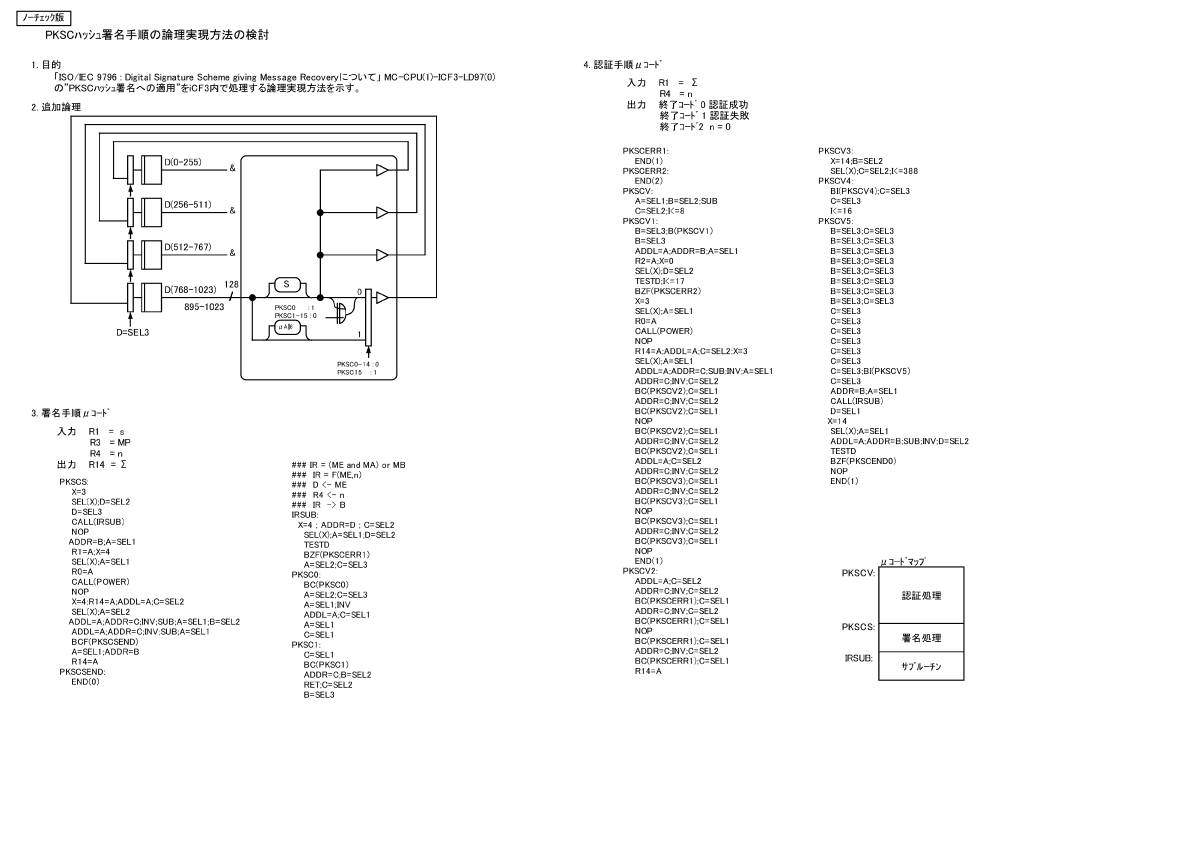

次の図は、その検討資料です。

画像は、クリックすると拡大表示されます。

工夫すれば論理を追加することなくマイクロコードだけで実装できるのではないかという意見を受け、

調査し実装を成功させた。1bitをXORする機能と1bitシフトの機能を駆使した。

ただし、この方法ではコード量が、かなり大きくなる問題があった。

このため最初はICF3のLSIのバージョンアップを考えていたのです。

マイクロコードを使って実装できないかという相談をされた時には

「マイクロコードの容量は512ワードなので、最悪、入りきらないことがあります。」

という返答をしました。結局、ギリギリ512ワードに入って、マイクロコードによる実装が成功したのです。

ゲート数ゼロの演算器

ハード編でゲート数ゼロのOR/XOR/AND演算器について説明をした。

ソフト編では具体的なマイクロコードを示す。シミュレータでも動作する。

D = B xor C (7サイクル)

A = !B A=SEL1;INV;ADDR=B

D = A or C ADDR=C;D=SEL3

A = !C A=SEL1;INV;ADDR=C

C = !D C=SEL2;INV;ADDR=D

D = A or B D=SEL3;ADDR=B

A = !D A=SEL1;INV;ADDR=C

D = A or C D=SEL3;ADDR=C

A = B and C (4サイクル)

B = !B B=SEL2;INV;ADDR=B

A = !C A=SEL1;INV;ADDR=C

D = A or B D=SEL3;ADDR=B

A = !D A=SEL1;INV;ADDR=D

|